DUV也能实现5nm,一种“新”思路

来源:内容由半导体行业观察(ID:icbank)编译自semiwiki,谢谢。

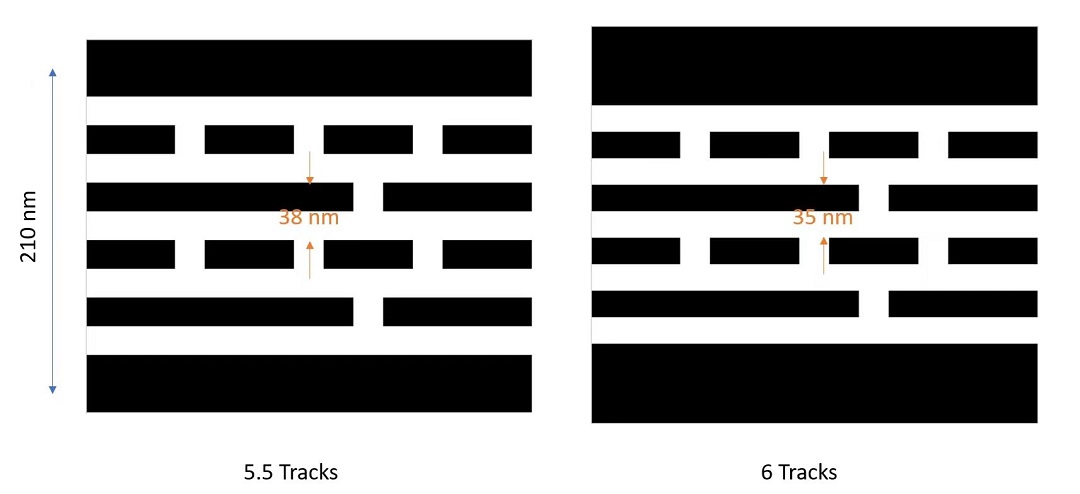

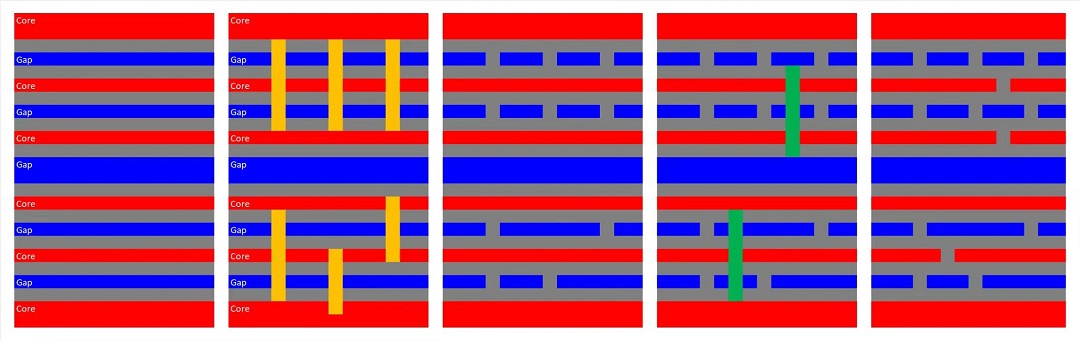

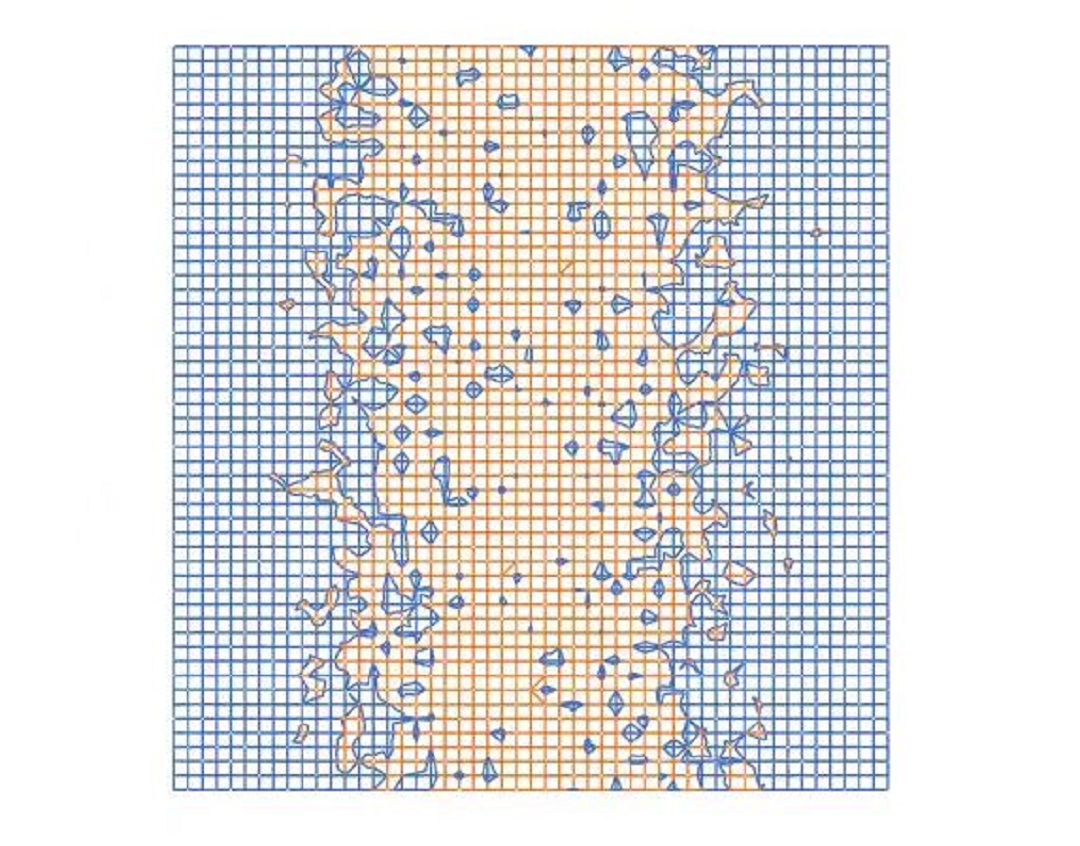

在 IEDM 2019 上,台积电发布了两种版本的 5nm 标准单元布局:5.5 轨道 DUV 图案化版本和 6 轨道 EUV 图案化版本 [1]。虽然没有明确说明金属间距,但后来对 5nm 产品(即 Apple 的 A15 Bionic 芯片)的分析显示,单元高度为 210nm [2]。对于 6 轨道单元,这表示金属轨道间距为 35nm,而对于 5.5 轨道单元,间距为 38nm(图 1)。仅仅 3nm 的间距差异对于图案化方法就很重要。如下所示,选择 5.5 轨道单元进行 DUV 图案化非常有意义。 图 1. 210 nm 单元高度意味着 5.5 条轨道的轨道间距为 38 nm(左),或 6 条轨道的轨道间距为 35 nm(左)。 将 7nm DUV方法扩展到5nm 5.5 轨道金属间距为 38 纳米,这是 DUV 双重曝光的极限。因此,它可以重复使用 7 纳米中使用的相同方法,其中 6 轨道单元金属间距为 40 纳米 [3]。这可以简单到自对准双重曝光,然后是两个自对准切割块,每个要蚀刻的材料(核心或间隙)一个(图 2)。切割块(每种材料)的最小间距为 76 纳米,允许单次曝光。 图 2. SADP 后跟两个自对准切割块(一个用于芯材料,一个用于间隙材料)。从左到右的工艺顺序为:(i) SADP(芯光刻后跟间隔层沉积和回蚀以及间隙填充;(ii) 切割块光刻以暴露要蚀刻的间隙材料;(iii) 重新填充切割块以填充间隙材料;(iv) 切割块光刻以暴露要蚀刻的芯材料;(v) 重新填充切割块以填充芯材料。在块形成后,可以部分蚀刻自对准通孔(未显示)[4]。 可以使用 SALELE [5] 代替 SADP。这将为间隙材料添加额外的掩模,因此总共需要四次掩模曝光。 低于38纳米间距:突破多重图案化障碍 对于 3nm 节点,预计金属轨道间距将低于 30nm [6]。任何低于 38nm 的间距都将需要使用更多 DUV 多重图案 [7]。然而,即使对于 EUV,也可以预期相当数量的多重图案,因为对于典型的 EUV 光刻胶,光电子扩散的最小间距实际上可以达到 40-50nm [8,9]。25nm 半间距 60mJ/cm2 曝光的边缘清晰度受到光子散粒噪声和光电子扩散的严重影响(图 3)。 图 3. 25 nm 半节距电子分布图像,入射 EUV 剂量为 60 mJ/cm2(吸收 13 mJ/cm2),7.5 nm 高斯模糊表示参考文献 [9] 中给出的电子扩散函数。使用 1 nm 像素,每个光电子有 4 个二次电子。 5nm适合所有人吗? 5.5 轨道单元利用 DUV 双重图案化技术,提供了一条从 7nm 到 5nm 的简单迁移路径。这可能是中国公司在 5nm 上赶上的较容易的方法之一,尽管这显然是他们能做到的极限。 参考 [1] G. Yeap 等人,IEDM 2019,图 5。 [2] https://www.angstronomics.com/p/the-truth-of-tsmc-5nm [3] https://fuse.wikichip.org/news/2408/tsmc-7nm-hd-and-hp-cells-2nd-gen-7nm-and-the-snapdragon-855-dtco/#google_vignette [4] F. Chen,自对准块重新分配和扩展以提高多重图案生产率,https://www.linkedin.com/pulse/self-aligned-block-redistribution-expansion-improving-frederick-chen-rgnwc/ [5] Y. Drissi 等人,Proc. SPIE 10962, 109620V (2019)。 [6] https://fuse.wikichip.org/news/7375/tsmc-n3-and-challenges-ahead/ [7] F. Chen,DUV 多重图案化向 3nm 的扩展,https://semiwiki.com/lithography/336182-extension-of-duv-multipatterning-toward-3nm/,https : //www.linkedin.com/pulse/extension-duv-multipatterning-toward-3nm-frederick-chen/ [8] F. Chen,为什么 NA 与 EUV 光刻中的分辨率无关,https://www.linkedin.com/pulse/why-na-relevant-resolution-euv-lithography-frederick-chen-ytnoc,https://semiwiki.com/lithography/344672-why-na-is-not-relevant-to-resolution-in-euv-lithography/ [9] T. Kozawa 等人,JVST B 25, 2481 (2007)。 参考链接 https://semiwiki.com/lithography/347246-application-specific-lithography-patterning-5nm-5-5-track-metal-by-duv/#comment-43825 *免责声明:本文及图片由文章作者原创。文章内容系作者个人观点,不做任何商业用途。南智光电仅作转载分享,若有任何异议或侵权,敬请联系,谢谢!